The course Advanced Topics on ASIC Implementation by Tampere University has come to its midpoint. The lecture part of the course is finished and the students are eager to start working on the lab assignment that covers the second half of the course.

There are 15 motivated students on the course – a nice tight group for the first implementation.

Motivation, contents

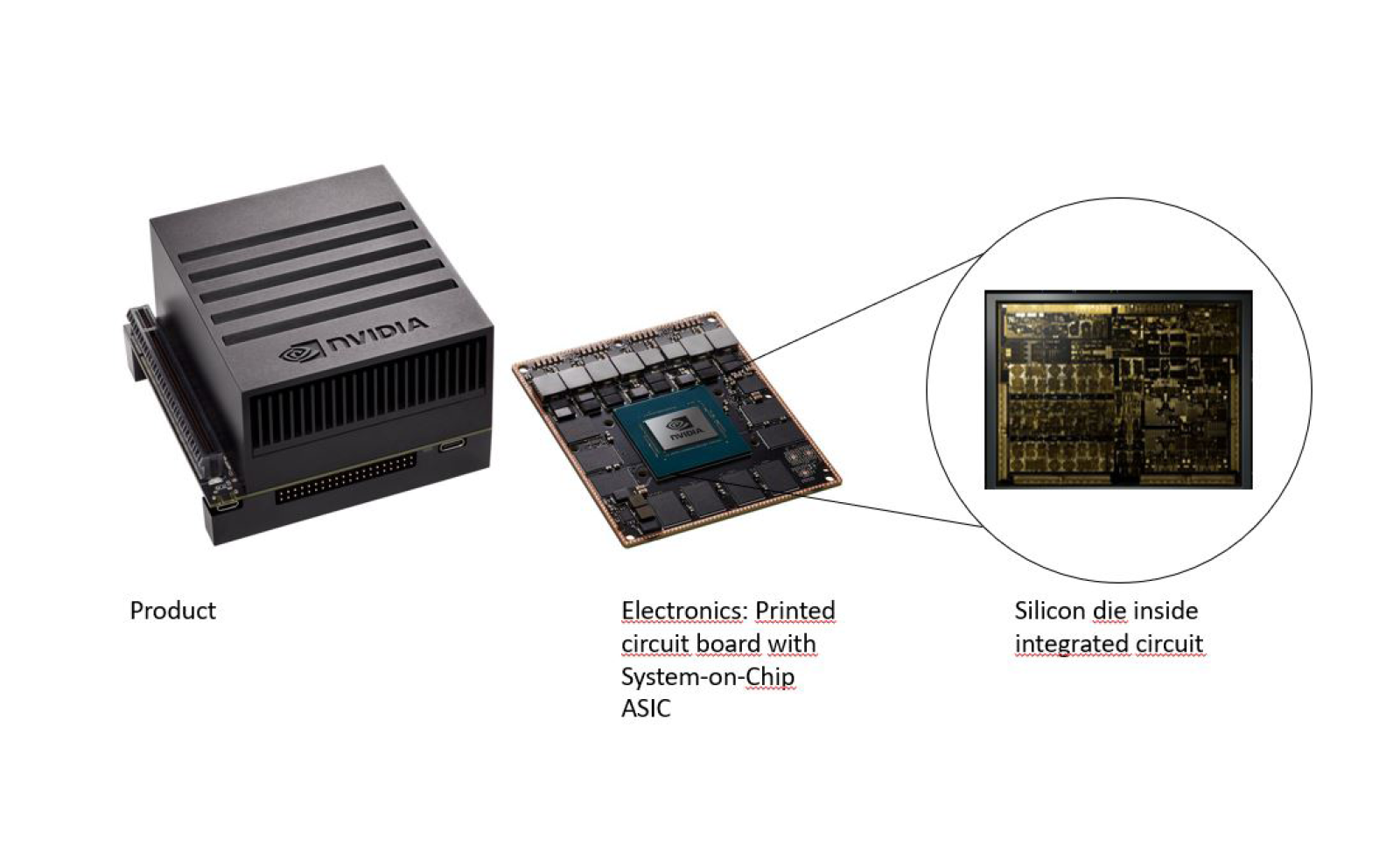

Tampere University has had a strong offering of digital design courses. Our curriculum presents a concise path all the way from small led blinkers to integration of multiprocessor platforms. Our courses have utilized Field Programmable Gate Array (FPGA) chips which are good for prototyping, but often in the industry setting the target platform is application-specific integrated circuit (ASIC) based implementation due to its performance and unit price costs advantage. Also, the academia on the field have moved toward ASIC based implementations to focus research where the challenges resides.

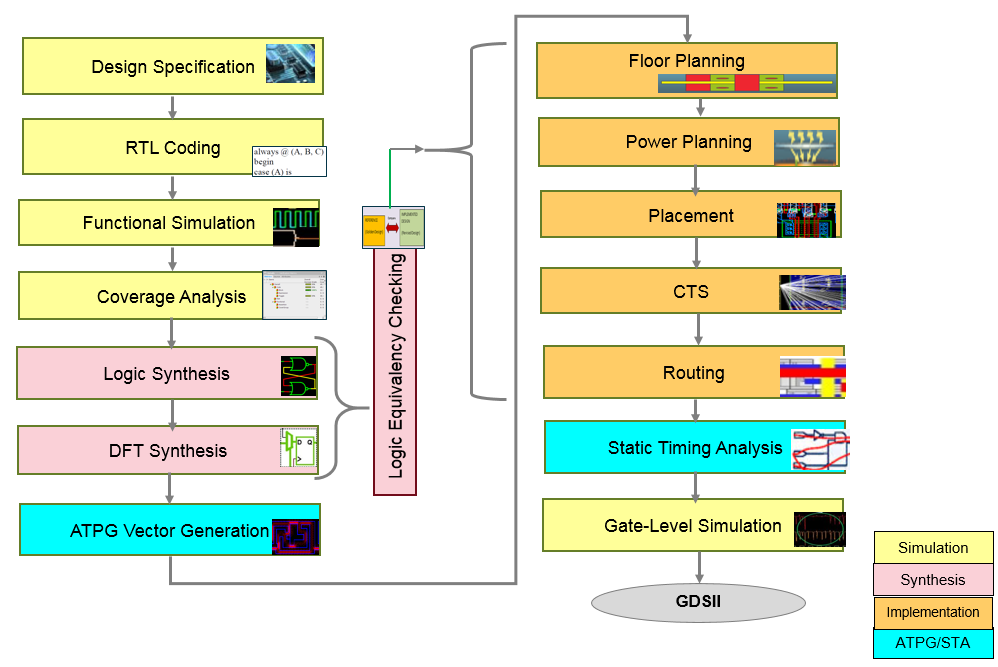

These needs inspired us to extend our education with a new course that covers the steps relevant for ASIC design. Luckily digital design for these different platforms, FPGAs and ASICs, share similar Design and Verification steps (yellow in the figure) in the beginning of the design process so students have the needed prerequisites from existing courses. After that ASIC specific steps come into picture (Marked on pink, orange and cyan). Eventually after multiple quality checks the design database (GDSII) is ready to be sent to fab for production. The production is something we can’t do in course context, but definitely the topic to return to in upcoming posts!

All these steps require separate tools and a vast knowledge of the tool flow. The success of an ASIC designer depends on various physical phenomena: delays in nanoseconds, capacitances in picofarads, and wire lengths in micrometers sound miniscule, but all of these must be managed for a working product. Otherwise, your mobile would be the size of a football field powered by a separate power plant.

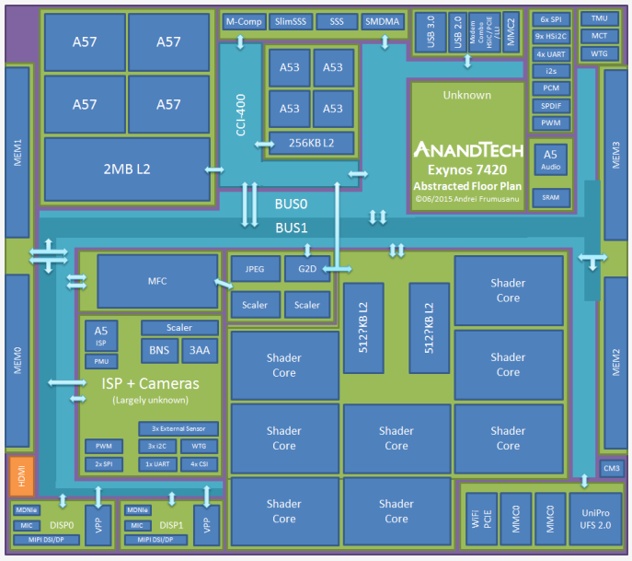

Modern ASICs consist of various submodules: even tens of CPU cores, co-processors, accelerators, and interfacing modules are all devoted to their specific tasks. Communication between those modules demands a complex interconnect network – a network-on-chip (NoC).

Source: https://www.anandtech.com/show/9330/exynos-7420-deep-dive/2

Due to importance of high-bandwidth interconnect and previous research and development by our group, we selected a NoC as the design to be focused on in our course labs.

Lectures, seminar presentations and labs

The course started with our own lectures on NoC basics. After the introduction, the first assignment for the students was to analyze and present a recent scientific article on SoC, Network-on-Chip, or ASIC technology domain. Students chose interesting articles on the progress of NoC research and we even had one presentation on a new unconventional transistor logic to replace the familiar CMOS gates. We want to thank all the presenters, also the teachers learned a lot!

Collaboration with various partners had an important role in the implementation of the course. As a result, we have had many interesting guest lectures by experts. Erno Salminen from Nokia gave us a double lecture introducing the ASIC synthesis and physical design steps form industry-scale project perspective. That was followed by lectures held by the experts from one of the leading Electronic Design Automation (EDA) tool companies, Cadence. Cadence gave us training about their tools and students also got access to the Cadence training platform where they have a wide catalog of online courses.

That gave student the needed knowledge to continue on practical side with the lab exercises. The labs will cover all the steps in the ASIC flow. The course will conclude in December with a second seminar presentation by the students. They will explain the power, performance, and area results they achieved for their implementation. Different results and approaches will surely raise interesting discussions!

Written by Arto Oinonen & Antti Rautakoura