SoC Hub was represented at the HiPEAC’s Autumn Computing Systems Week (14–17 October) where Esko Pekkarinen and Joonas Multanen, doctoral researchers at Tampere University, gave their presentations on their research topics. HiPEAC is a European network in high-performance computing architectures which also addresses embedded and cyber-physical systems such as IoT.

Esko Pekkarinen is a member of System-on-Chip Research Group at the Faculty of Information Technology and Communication Sciences. The research group is the developer of Kactus2, which is the most famous open source IEEE 1685 IP-XACT tool. After the first release in 2011, it has become widely used in hundreds of companies. At SoC Hub, Esko has versatile duties. Mainly he contributes to IP-XACT modeling, project management and supporting the IT infrastructure.

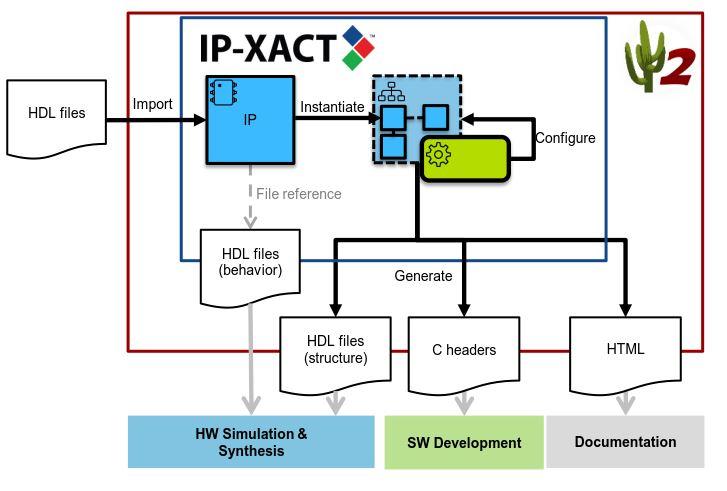

At the Computing Systems Week, Esko gave a presentation on “Modelling RISC-V architecture in Kactus2”. IP-XACT is the most prominent standard for high-level models and reuse of intellectual properties, yet the adoption has been slow. In the SoC Research Group’s experience, the modeling work is unappealing for the hardware designers due to large legacy code bases compared to the perceived benefits in the short-term. In their recent research work, the research group took an open-source implementation of a RISC-V microprocessor as is and packaged it with Kactus2. Here IP-XACT is used to manage the different RISC-V configurations and to provide clear interfaces thus easing the integration work. The SoC Research Group provides the model as a public IP-XACT example, which to this day are very scarcely available. Based on the modeling experience, several common cases which may hinder the transition from hardware description language to IP-XACT were identified and means to mitigate their impact were proposed. The research group’s future work will be on improving the tool automation and increasing the IP-XACT modeling scale from a single microcontroller to a full system-on-chip.

See the slide show for Esko’s presentation here

Joonas Multanen is a member of the Customized Parallel Computing Group (CPC) at the Faculty of Information Technology and Communication Sciences. CPC’s main research focus is on design and programming methodologies of customized parallel computing platforms and real time implementations of challenging algorithms. Joonas’s doctoral thesis aims to increase the energy-efficiency of instruction streams in processor cores. The methods developed in the thesis could be used in future computing systems to improve battery lifetime or reduce heat generated by the devices.

At SoC Hub, Joonas is one of the developers of the digital signal processing (DSP) subsystem. His presentation at the Computing Systems Week was an introduction to TTA-based Co-design Toolset (TCE) which is used to design, generate, program, and verify the DSP subsystem. The open-source TCE can be downloaded at http://tuni.fi/cpc.

See the slide show for Joonas’s presentation here

Watch the recording of the Computer Science Week session here.