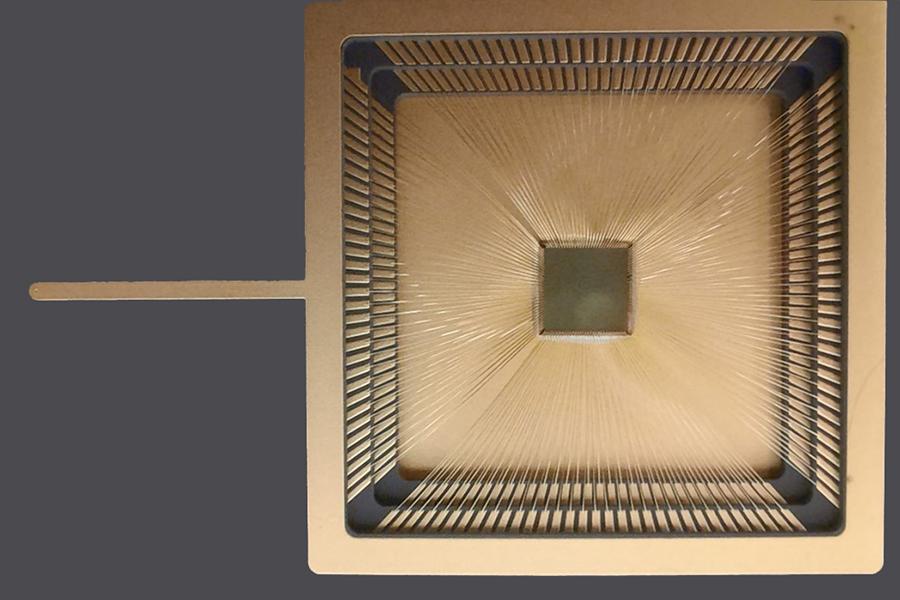

The Ballast chip wired with golden strings to the package that will be soldered to the printed circuit board. Photo: Tampere University.

At the end of 2021, the tape-out of Ballast, the first SoC (System-on-Chip), was completed by the SoC Hub ecosystem project. The project is based on a collaboration between Tampere University and businesses. The physical chip samples have now arrived in Tampere, and the chip has been tested to be functional.

The result of the close collaboration of the SoC Hub consortium is a System-on-Chip named Ballast which was manufactured by TSMC in Taiwan. When the chips arrived in Europe, some of them were packaged by the Imec research institute and sent to Tampere.

The preparations for the chip’s arrival had been ready for some time since Ballast was supposed to arrive in Tampere earlier this spring. However, the delivery was delayed because of the packaging. In early June, the wait was over when hundred SoCs arrived at Tampere University.

After an SoC is produced, the first testing task is to wake up the chip.

“Waking up a chip is exciting. Even though the plans are in order, some surprises often occur and the visibility into the chip is very limited. It is not at all trivial to get the processor to run the code,” says Ari Kulmala, Professor of Practice of System-on-Chip Design at Tampere University.

However, the Ballast chip woke up already in only two working days. The processors are able to start to execute a traditional led blinking program. The successful wake-up shows that the design of the chip was successful. For testing Ballast, a custom “Granite” printed circuit board was made, which will also act as the development kit of the chip.

Next, the testing process will proceed to detailed subsystem tests and performance measurements.

The next SoC is already being developed along with Ballast applications

Ballast is a versatile and multipurpose System-on-Chip which can be used in different applications.

“After thorough testing, we will start working on demonstration applications with our business partners. One example of these is a machine learning application for vehicle classification,” says Professor Timo Hämäläinen.

The chip was manufactured using TSMC’s recent 22nm Ultra Low Leakage process, which is especially well suited for IoT and Edge devices. Ballast contains several different RISC-V CPU cores, a Digital Signal Processor, an AI accelerator, rich sensor-like interfaces, and an extension interface to FPGA. A full software framework has also been implemented.

The design of Ballast is part of the SoC Hub consortium project funded by Business Finland. The partners include Tampere University, Nokia, CoreHW, VLSI Solution, Siru Innovations, TTTEch Flexibilis, Procemex, Wapice and Cargotec.

SoC Hub will develop three chips by the end of 2023. The development of the second chip is underway and the tape-out is expected later this year.

”System-on-Chip design is essential for technological development and it requires efforts from both research organisations and businesses as well as collaboration between them. This achievement by SoC Hub shows that right things for this industry are being done in Tampere,” says Kari Leino, Ecosystem Lead at Business Finland.