The chip design process is in continuous evolution due to heavy competition between companies. Chip designs themselves evolve over time to increase their capabilities and to improve their characteristics. The design process is heavily iterative. Designs advance with small increments building on known foundation. This leads into a situation that allows novel approaches to be highly disruptive and potentially having a significant impact on the whole industry.

Integrated circuit (IC) design concepts originate from the 1960s when a single chip could house some tens or a hundred transistors. Mapping the locations and wires at this point is done by engineer manually. Circuits grew as the demand for more complexity to be integrated grew. There was demand for documenting the circuit internals and hence Hardware Description Languages (HDLs) were created. Manual design effort started to reach its practical limits at this point.

During the 1980s came a big design revolution: Logic Synthesis. Instead of having designers do conversions from logic to circuits manually, came automated tools that did the process for the designer. This created a major leap in productivity. During this time, a few of the most prominent HDLs were created: VHDL and Verilog. Designers used these languages to describe the circuit functionality, which was then transformed into a transistor layout by tools. IC design is still done today using this process and these languages.

While programming methodologies have evolved and changed over the decades, very little conceptually has changed in circuit design from the start of logic synthesis era. Circuits themselves have become a lot more complex, even in just a few years recently. Productivity is leveraged from chip architectures, design practices and faster feedback times from tools and automation. Productivity increasing methods like agile development are still relatively unused concepts due to circuits being physical devices and the iteration time being long.

Over the past decade, new techniques to replace or improve the logic synthesis process have been introduced. These include higher level design frameworks and languages including techniques such as HDL generators and synthesis from other languages to HDL. These techniques are improving and proving themselves but are not yet mainstream in IC design.

Over the past decade, new techniques to replace or improve the logic synthesis process have been introduced. These include higher level design frameworks and languages including techniques such as HDL generators and synthesis from other languages to HDL. These techniques are improving and proving themselves but are not yet mainstream in IC design.

Tampere University teaches chip design techniques on various courses. Most prominent of these is the Logic Synthesis course. As the name suggests, this course teaches chip design process with an HDL language. For new hardware developers, this is the most important topic and passing the course with good grades has traditionally been very valued among companies. Furthermore, advantages of synthesis to HDL languages are well understood. One such technique is a high-level synthesis (HLS) from generally C or C++ language. Tampere University offers a course on this technique as well. It bears the techniques name, High-level synthesis.

As part of SoC Hub research, we published a survey that investigated what kind of higher-level language frameworks are available. The aim of this survey is to investigate if we could use a language that would enable new programming paradigms and higher-level features to be used with circuit design. Such higher-level language could have a significant impact on designer productivity, and it could facilitate a new revolution in chip design practices. [1]

Our survey confirms that there are multiple choices for higher level language and such languages can be adopted to increase productivity. Benefit of HLS technique was already recognized before the survey. As such, our specific focus was to investigate the potential to use functional programming paradigm with a high-level language.

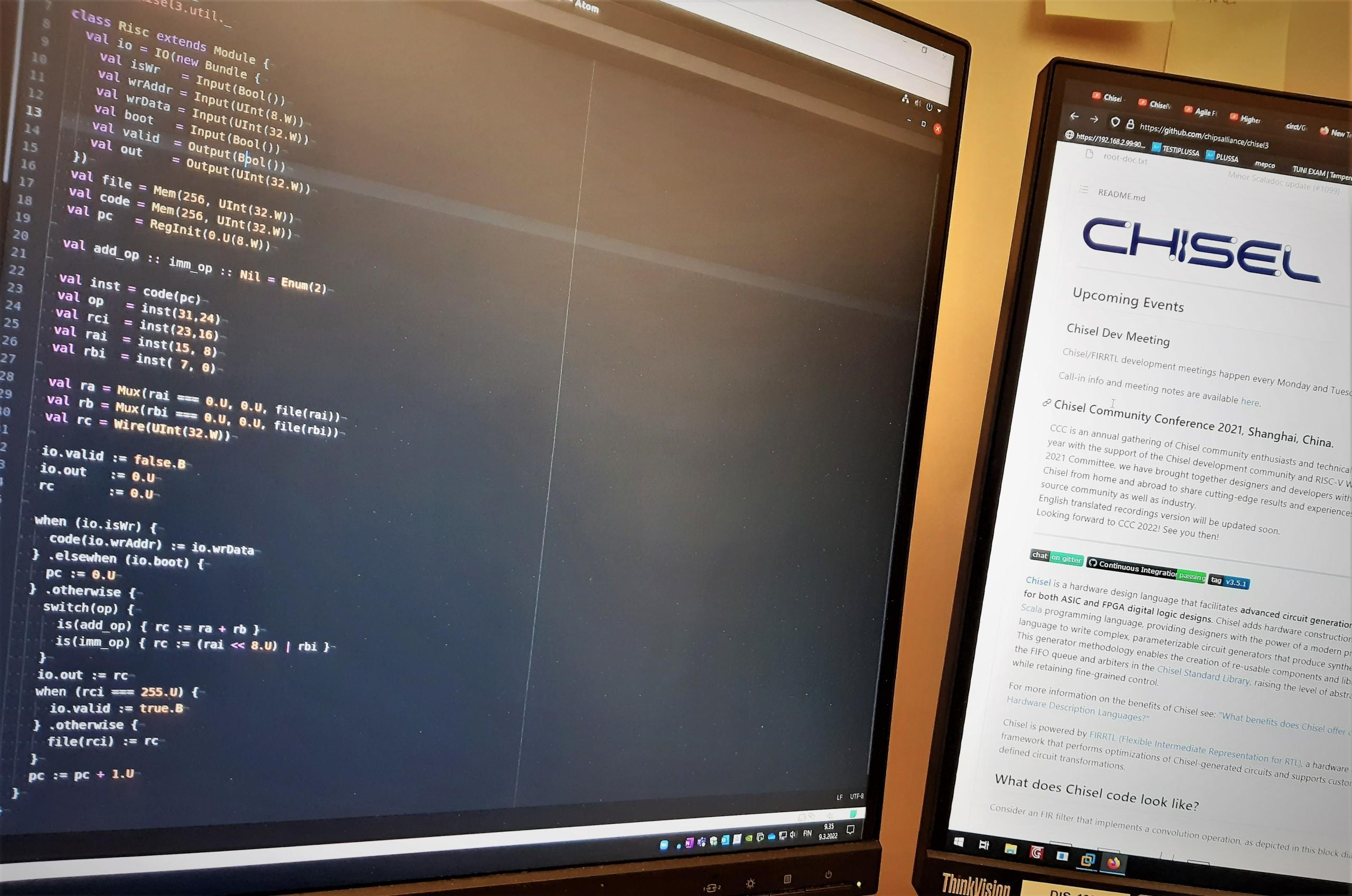

The survey found that Scala-based Chisel-language seems to be currently the most prominent new solution for circuit design. It enables features of the Scala to be used in domain specific way. As Scala is a multiparadigm programming language, it means that it enables both object-oriented and functional paradigms. This allows hardware designers to adopt new programming styles that could be highly beneficial.

Chisel has an active development community around it, and there are a lot of publications about using the language. Some very prominent companies have also expressed their support and interest in the language. Most importantly, Chisel has been successfully used to create many IC designs all the way to physical devices.

With the advantages of modern languages, maybe it is finally time to shift out of using nearly 40-year-old design languages and practices.

Written by Matti Käyrä

[1] M. Käyrä and T. D. Hämäläinen, ”A Survey on System-on-a-Chip Design Using Chisel HW Construction Language,” IECON 2021 – 47th Annual Conference of the IEEE Industrial Electronics Society, 2021, pp. 1-6, doi: 10.1109/IECON48115.2021.9589614.