The Unit of Computing Sciences at the Faculty of Information Technology and Communication, Tampere University, opens a University Instructor position in System-on-Chip Design.

SITE DESCRIPTION

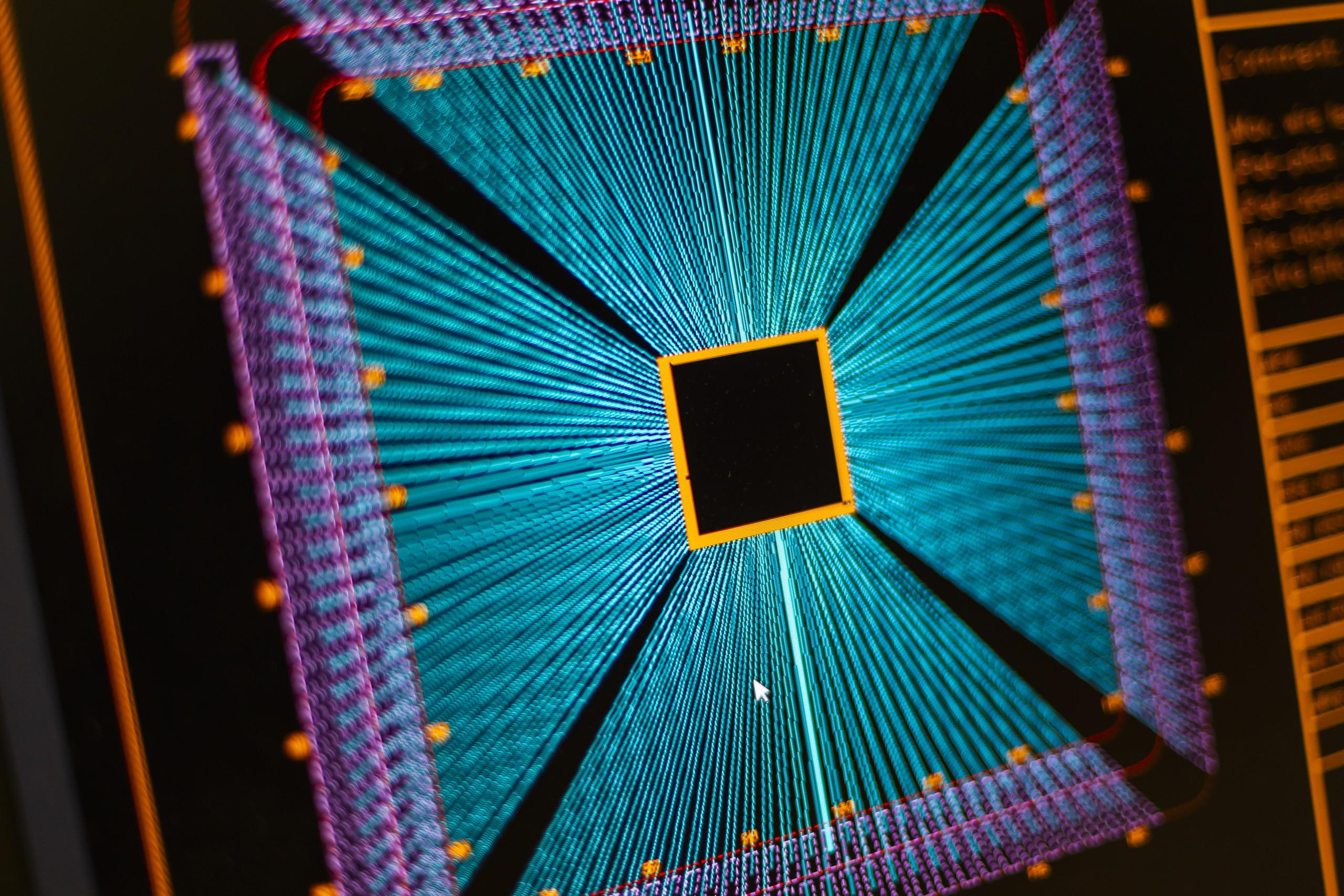

Join the cutting-edge world of chip design at Tampere University, located in the vibrant Tampere City within the Pirkanmaa region of Finland. Our esteemed institution aims to enhance the design excellence of chips. Tampere University was recently granted a six-years Academy of Finland Profiling action “Silicon2Action” combining System-on-Chip, Wireless Communications, and Robotics and System-on-Chip Hub (SoC Hub) was started in 2019 to become one of the top design sites in Europe. The success is based on a three-decade expertise on microelectronics, FPGA, and DSP based multiprocessor system designs in collaboration with industry.

Recently, Tampere University, Tampere City, and Pirkanmaa region released Chips from Finland initiative leading to strengthening EU’s Chips Act design excellence in the region that has strong business cluster around wireless communications, intelligent machines, and imaging. Nokia designs the most advanced chips in Europe for 5G on the latest IC technology nodes in Finland, and Industry 4.0 companies has big potential for custom chips differentiating and securing the competitiveness. To meet industrial challenges, SoC Hub focuses on large, top quality prototype chips in the smallest geometries and aiming at high technology readiness level TRL6 onwards. SoC Hub created a unique co-working model in which over 70 experts from the university and companies carry out the SoC design daily. The promise of one large SoC per year has been proven with over 130M transistor chips from 2021. We use open source and custom Intellectual Property (IP) blocks and a mixture of open source and commercial EDA tools.

Join us at Tampere University and be part of an exceptional team which drives innovation, fosters collaboration, and shapes the future of chip design.

JOB DESCRIPTION

We are seeking a System-on-Chip Design University Instructor to join our team in Tampere University. The current study line is described in our blog on how to become a System-on-Chip design expert. We are starting a new focused Master’s study module on System-on-Chip starting in Fall 2024 and bringing new courses on digital ASIC backend design. Students will create tape-out ready chips and perform bring-up of the manufactured samples as a teamwork project. Our promise to students is hands-on end-to-end knowledge of real-scale SoC design, with concrete goals backed up by leading companies in Tampere region.

The University Instructor contributes to the overall SoC study line planning and takes responsibility of agreed courses. The University Instructor is expected to create teaching materials and exercises, carry out learning events and conduct student supervision and grading. The work includes setup of teaching and tool environment and expert level communication with ASIC technology and EDA tool vendors. Significant part of the work is participating in research and education development projects to stay at the edge of technology development.

The teaching is carried out in teams, in which hourly paid teaching assistants and SoC research staff support the University Instructor. Tampere University has state-of-the art EDA tools and ASIC technologies, as well as the most current teaching environments including automated grading systems. Excellent connections to companies create an exciting environment to train both degree students and life-long learners.

REQUIREMENTS

For the University Instructor position, we require:

- Working proficiency in the Finnish and English language.

- Applicable Master’s degree

- Ability to provide high-quality teaching and instruction

- Good command of Finnish and English language

- Good cooperation and interaction skills

- Proven expertise or professional experience in System-on-Chip design

The following will also be taken into account as advantages in the selection process:

- Studies in pedagogy, pedagogic competence, and experience in curriculum development

- Involvement in teaching-related networks and activities

- Industrial collaboration experience, demonstrating the ability to bridge academic and industry perspectives

- Previous experience on digital ASIC design projects and teaching experience in the field are appreciated.

The recommended skills include, for example, some of the following:

- HDL tools (VHDL, Verilog, SystemVerilog)

- High-Level Synthesis and SystemC based tools (C++)

- Repositories (Git), continuous integration (CI), integrated documentation (markdown) and ticketing systems

- Knowledge on ASIC technologies and design libraries

- Experience on EDA tools (RTL tools, synthesis, digital ASIC backend, verification and testing)

- Verification methodologies

- ASIC design flows, manufacturing logistics and lab testing

- Knowledge on open-source IP-blocks (RISC-V)

WE OFFER

The position will be filled on a permanent basis and the start date will be January 2024 or as mutually agreed. The salary will be based on Finnish University Salary System which applies to teaching and research staff. According to the criteria applied to teaching and research staff, the position of a University Instructor is placed on levels 5-6 of the job requirements scale.

We offer you the opportunity to join our dynamic and innovative international community. As a member of staff at Tampere University, you will enjoy a range of competitive benefits, such as occupational health care services, flexible work schedule, versatile research infrastructure, modern teaching facilities and a safe and inviting campus area with low-cost sports facilities at your disposal. We provide a personal fund to spend on sports and cultural activities in your free time and we also have a “one working hour on sports” program and a subsidized bike benefit scheme.

Please read more about working at Tampere University. You can also find more information about us and working and living Tampere by watching our video: Tampere Higher Education Community – our academic playground.

HOW TO APPLY

Please submit your application through Tampere University’s online recruitment system. The closing date for applications is 22nd of September 2023 (at 23.59 EEST / UTC +3). Please write your application and all accompanying documentation in English and attach them in PDF format only.