In devices powered with batteries or other limited energy sources, energy-efficiency is clearly one of the most important design considerations. In larger scale, good energy-efficiency is crucial to keep the power consumption of the computers down – which has an immediate practical impact to the required cooling devices and to the electricity bills of data centers. In an even larger (and a more important) picture, as computing becomes increasingly pervasive, the size of its energy footprint keeps increasing; it is estimated that the ICT sector will consume up to 20% of all global electricity by 2025 1, having a surprisingly large effect to the global warming challenge we are now struggling with.

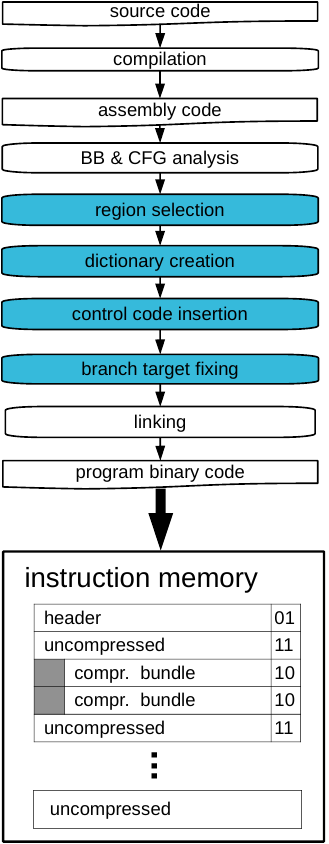

Figure 1: Programmable dictionary compression flow and an example of instruction placement in memory.

So called fixed-function hardware accelerators are designed to perform a single computation task or a limited variation of tasks very efficiently. Their performance, size and energy consumption can be highly optimized by implementing the required functionality directly onto silicon as an application specific integrated circuit (ASIC). The flip side is that the tasks not fitted to the accelerator may perform poorly or cannot be implemented at all after the design including the accelerator has been manufactured on silicon. The ”post manufacture flexibility” can be enhanced by making some of the internal components software programmable. Programming means that a user of the device defines the computing tasks as sequences of smaller actions called ”instructions” – a special language which the processor understands.

Unfortunately, there is no free lunch. Adding programmability – or flexibility of any kind – always incurs overheads which also increase energy consumption of the device, decrease the speed of execution and result in a larger silicon area used by the microchip. To this end, one of the research directions of our research group, Customized Parallel Computing research group (CPC) is to research techniques that can reduce the energy impact of flexibility in computing devices. The goal is to make flexible co-processors closer to the energy efficiency of the fixed function accelerators, which in turn helps in reuse of the manufactured silicon and, for example, enables post-manufacture application logic bug fixing.

The most recent outcome from this research track was presented in the ICCD 2020 conference 2. In this paper we studied code compression, which can be used as a way to improve the instruction stream energy-efficiency. Code compression reduces the amount of traffic between the processor and the energy-hungry memories that store the instructions. This is achieved by representing often occurring instructions in a shorter format. The published method uses multiple parallel dictionaries to store often occurring parts of instructions. One of the novel aspects in this work is that these dictionaries can be updated on the fly during the program’s execution, allowing enhanced compression ratios for the instruction mixes found in different program phases, leading to significant reductions in the instruction stream energy overhead.

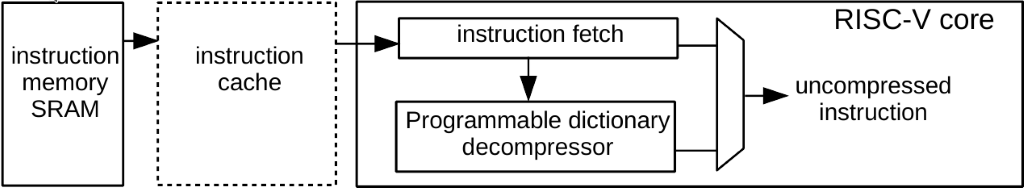

In the ICCD publication, the proposed code compression was implemented on a “general-purpose” low power consumption processor implementing the RISC-V instruction-set architecture. As the developed method is not tied to any processor architecture, it is now being evaluated in a multi-issue Digital Signal Processor (DSP) designed with OpenASIP tools maintained by the group. The initial results are very encouraging.

Figure 2: Example processor system using the programmable dictionary compression.

For individual groups, manufacturing actual ASICs is often not feasible, as it is an expensive and a risky endeavour. Being a part of the SoCHub community, the CPC group has better possibilities to demonstrate novel research in practice. We hope to utilize the programmable dictionary compression technology in a future SoC Hub microchip project.

This work has been funded by Tampere University of Technology Graduate School and Academy of Finland (decision #331344). This project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No 783162 (FitOptiVis). The JU receives support from the European Union’s Horizon 2020 research and innovation programme and Netherlands, Czech Republic, Finland, Spain, Italy.

Written by Joonas Multanen and Pekka Jääskeläinen