The third System-on-Chip by the SoC Hub consortium has now been sent to manufacturing. An ambitious chip development goal has been reached, but the work of SoC Hub will continue as the fourth chip is already under planning.

“In 2020, we started chip development from scratch and set up the necessary infrastructure, design flow and agreements as well as the chip template itself. Developing one chip per year is not an easy task, but we can proudly say that we have reached our goal,” says Timo Hämäläinen, Professor of Computer Engineering at Tampere University.

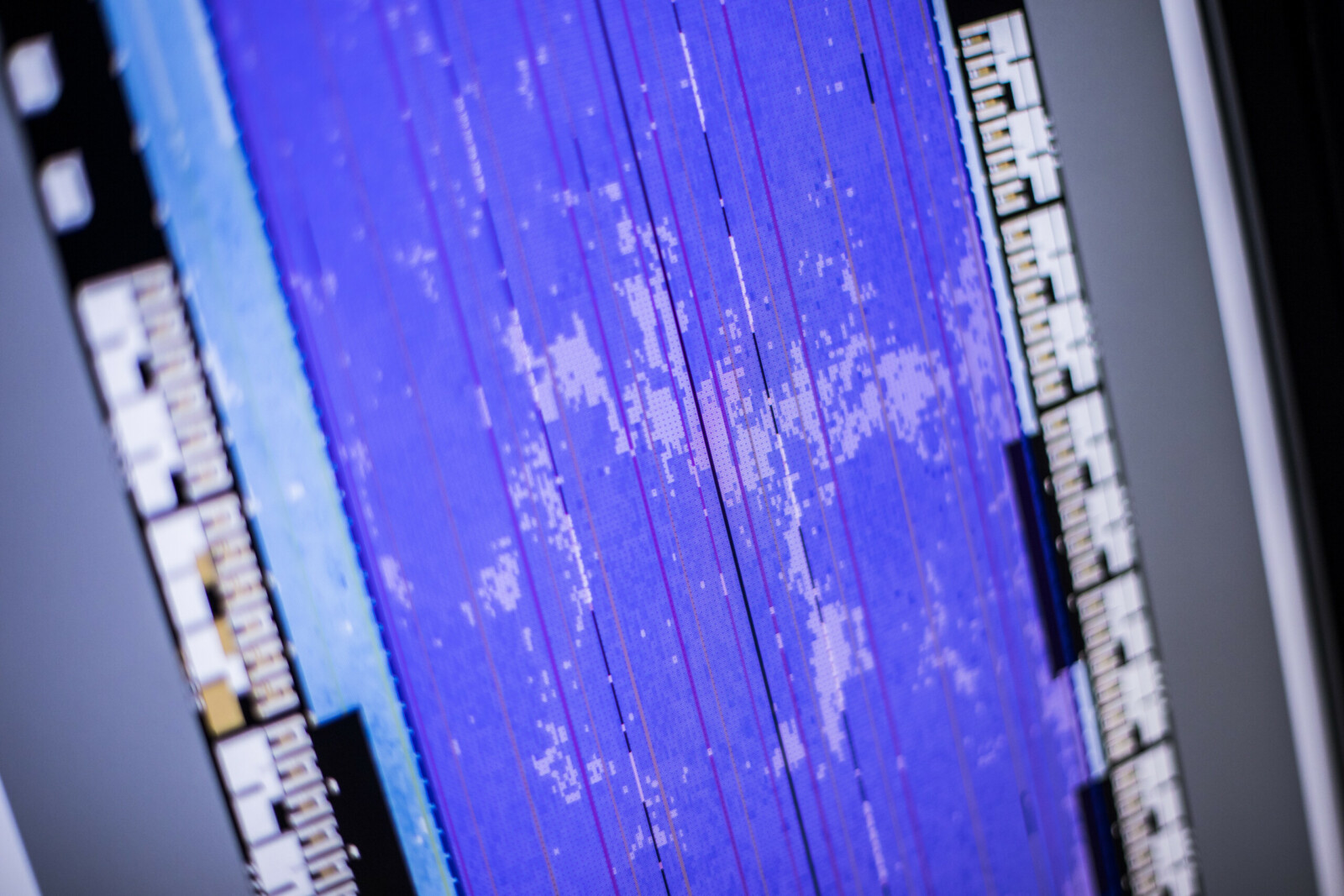

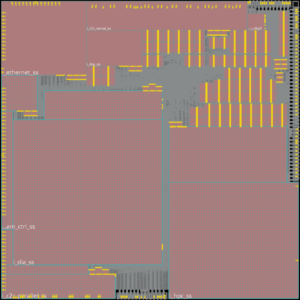

The new chip called “Headsail”, which has just been sent for manufacture at TSMC, is the most complex one so far. It includes a whopping 330 million transistors and IPs, such as the 4-core 64-bit RISC-V sub-system, Deep-Learning accelerator and much more. The complexity is almost unforeseen in open source-based academic chips which are also of commercial grade quality.

“Chip development has been very fast. This project focused on a rapid design flow time and increasing agile practices and we were able to design Headsail faster than previous projects despite the complexity of the chip”, says project manager and chip architect Antti Rautakoura from Tampere University. “As planned, we also benefitted from our novel IP-XACT based design automation tooling,” he adds.

“This is the peak of our collaboration and hard work of three years. The overall expertise has much increased in these three years and, apart from the expertise on complex digital SoC design, we have also invested in critical mixed-signal IP development,” Rautakoura says.

Developing a common chip template has been an integral part of the project. After these experiences, SoC Hub will focus more on the applications that will guide SoC development.

As with the previous chips, the project team will execute the wake-up of the Headsail chip once it arrives from manufacture. At the same time, the fourth chip is already being planned.

Headed by Tampere University and Nokia, the consortium comprises CoreHW, VLSI Solution, TTTEch Flexibilis, Procemex, Wapice and Cargotec as partners.

The future of SoC development in Tampere will build on the experiences of the project

SoC Hub is largely an ecosystem for SoC design, and it includes several projects.

“Our main goal is to keep designing SoCs, IPs and design automation for targeted applications. Next, we aim at 12 and 7 nanometre technologies. So far, this project has offered invaluable learning opportunities for the companies and individual experts. We want to widen our collaboration model beyond this consortium,” says Ari Kulmala, Professor of Practice in System-on-Chip Design at Tampere University.

Expanding the SoC ecosystem is also essential in terms of the EU Chips Act activities. Tampere University is deeply involved in plans to establish a System-on-Chip design Centre of Excellence in Finland.

“For increasing European technological sovereignty and competence, co-creation work and industry-academia co-operation are key,” Kulmala adds.

In Tampere, strengthening System-on-Chip design education will now be in the focus more than ever. Tampere University is starting a new advanced study module on System-on-Chip design in the autumn of 2024 and creating new courses on digital ASIC backend design. The students will get hands-on end-to-end expertise of real-scale SoC design, with concrete goals backed up by leading companies in the Tampere region.